FPGA는 본질적으로 방대한 양의 병렬 연산을 수행하는 데 최적화된 하드웨어 가속기입니다. FPGA는 Distributed RAM 및 Block RAM(BRAM,URAM)과 같은 On-chip memory를 내장하고 있어, 소용량의 데이터 저장이나 고속 데이터 버퍼링에 활용됩니다.

그러나, 이들 On-chip memory의 총 용량은 일반적으로 수십 메가비트(MB)에서 최대 수 백 메가비트 수준에 머물러 있어, 기가바이트(GB) 단위의 대규모 데이터를 처리해야 하는 애플리케이션에서는 한계가 존재합니다. 따라서, FPGA의 On-chip memory의 한계를 극복하고 대용량 데이터를 처리하기 위해 외부 DDR (Double Data Rate) 메모리를 활용하는 것은 고성능 FPGA 시스템 설계에 있어 필수적인 요소입니다.

예를 들어, 고해상도 영상 프레임이나, 머신러닝 모델의 가중치 등 대규모의 데이터를 저장하기 위해서는 외부 DDR 메모리 연결이 필요합니다.

DDR 메모리 유형과 선택

FPGA에 연결되는 DDR 메모리 기술은 다양한 유형으로 분류되며, 각각의 기술적 특성은 성능, 전력 소모, 비용 등 설계의 핵심적인 트레이드 오프에 직접적인 영향을 미칩니다. 설계자는 애플리케이션의 요구사항에 따라 가장 적절한 메모리 유형을 신중하게 선택해야 합니다.

| 메모리 유형 | 전압 | 최대 데이터 속도 | 모듈당 채널 수 | 주요 응용 분야 |

|---|---|---|---|---|

| DDR3 | 1.5V | 최대 2,133 MT/s | 1 | 일반 컴퓨팅, 영상 처리 |

| DDR4 | 1.2V | 최대 3,200 MT/s | 1 | 고성능 서버, DSP, AI |

| DDR5 | 1.1V | 최대 8,400 MT/s | 2 | 차세대 서버, 데이터센터 |

| LPDDR4/4X | 1.1V / 0.6V | 최대 4,266 MT/s | 2 | 모바일, 배터리 구동 임베디드 |

| HBM2e | 1.2V | 최대 3.2 Gbps/핀 | 8 | AI 가속기, HPC |

여기서, MT/s는 MegaTransfers per second의 약자로, 초당 백만 번의 데이터 전송을 의미합니다. DDR 메모리는 클럭의 상승 엣지(rising edge)와 하강 엣지(falling edge) 양쪽에서 데이터를 전송합니다.

예를 들어, DDR4-3200은 클럭 속도가 1600 MHz이고, 데이터 전송 속도가 3200 MT/s라는 것을 의미합니다. 여기에서 대역폭(Bandwidth)은 데이터 전송 속도(MT/s)에 메모리 채널의 비트 수를 곱한 값으로, 초 당 전송할 수 있는 데이터의 양을 나타냅니다. 채널의 비트 수는 FPGA 설계에 따라 16비트, 32비트 또는 64비트로 다양할 수 있습니다.

- 대역폭(MB/s)=MT/s * 채널의 비트 수

설계 목적에 따른 메모리 선택

대역폭 및 성능: 레이더, AI와 같은 고성능 디지털 신호 처리(DSP) 시스템에는 DDR4 또는 DDR5가 권장됩니다. HBM은 DDR5 대비 최대 18배 빠른 대역폭을 제공하여 궁극적인 성능이 필요할 때 고려됩니다.

전력 효율: 배터리로 구동되는 임베디드 시스템에는 LPDDR이 최적의 선택입니다. 흥미로운 점은 원래 모바일 기기용으로 개발되었던 LPDDR이 최근 데이터센터 시장에서 주목받고 있다는 사실입니다. 전통적으로 서버용 메모리는 안정성과 성능을 최우선으로 고려하여 LPDDR보다 안정적인 DDR D램을 채택해 왔습니다. 그러나 최근 전력 효율성이 중요한 화두로 떠오르면서, 설계자는 성능과 안정성이라는 전통적인 가치와 전력 효율이라는 새로운 가치 사이에서 전략적인 트레이드오프를 결정해야 하는 상황에 놓였습니다. 이 현상은 미래의 FPGA 기반 데이터센터 시스템 설계에서 ‘전력당 성능(Performance-per-watt)’이 핵심 지표가 될 것임을 시사합니다.

DDR 메모리 모듈과 칩

DDR 메모리 칩: DDR 메모리 칩 하나는 보통 x8 (8비트) 또는 **x16 (16비트)**의 데이터 버스 너비를 가집니다. 이는 하나의 칩이 한 번에 8비트 또는 16비트의 데이터를 주고받을 수 있다는 것을 의미합니다.

DDR 메모리 모듈 (DIMM): 우리가 컴퓨터에 장착하는 메모리 스틱을 DIMM (Dual In-line Memory Module)이라고 부릅니다. 이 모듈은 여러 개의 DDR 메모리 칩을 병렬로 연결하여 구성됩니다. 대부분의 PC용 메모리 모듈은 8개의 8비트 칩을 사용하거나, 4개의 16비트 칩을 사용하여 총 64비트의 데이터 버스 너비를 만듭니다. 이는 CPU가 한 번에 64비트의 데이터를 메모리와 주고받을 수 있도록 해줍니다.

작은 크기의 FPGA 시스템에서는 DIMM 형태가 아닌, DDR 메모리 칩 여러 개를 사용하는 방식을 사용할 수 있습니다. 이 경우 메모리 모듈이 아닌, 메모리 칩을 1개, 2개 또는 4개로 연결하게 됩니다.

FPGA-DDR 인터페이스 구현 방법론

FPGA와 DDR 메모리 간의 인터페이스는 수많은 핀에서 고속 신호의 지연 시간을 정밀하게 일치시켜야하는 복잡한 기술이 필요합니다. 이러한 문제를 해결하기 위해, FPGA 벤더사들은 표준화된 IP (Intellectual Property) 코어 솔루션을 제공합니다.

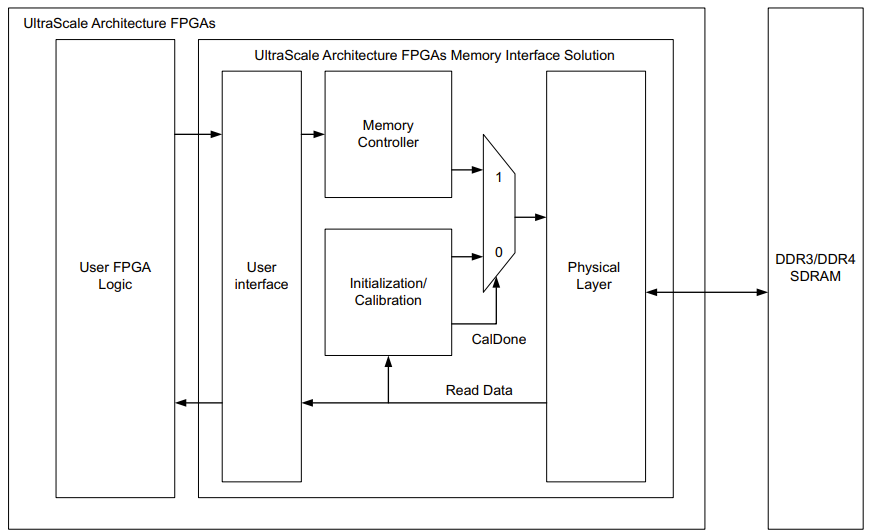

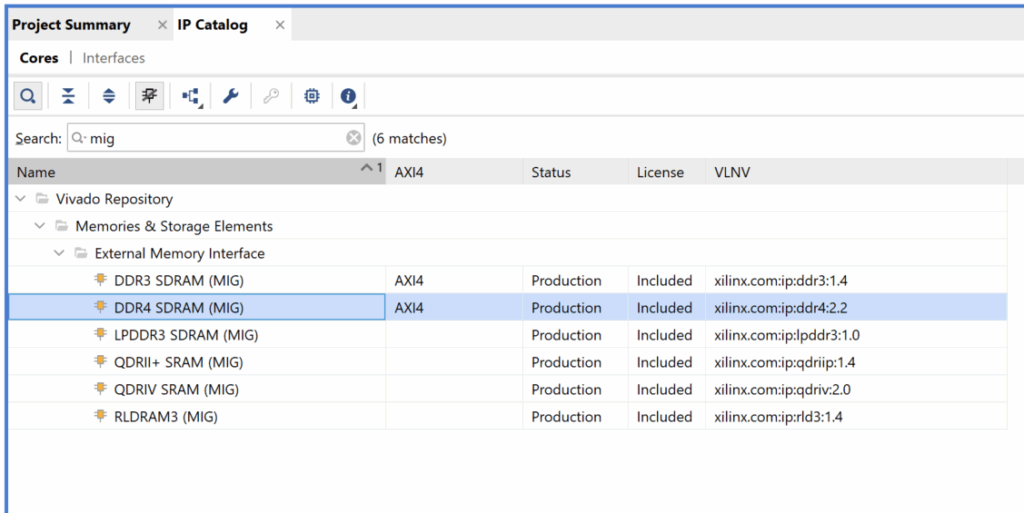

AMD/Xilinx는 Memory Interface Generator (MIG) IP 코어를 제공합니다. 이 코어는 메모리 초기화, 뱅크 관리, 명령 재정렬, 오류 정정 코드 등 고성능과 신뢰성을 보장하기 위한 복잡한 하위 레벨의 기능을 자동으로 처리해줍니다. Vivado IP Catalog를 통해, 디자인에 통합할 수 있습니다. 사용자는 IP를 통해 복잡한 PHY 와 컨틀롤러 기능을 직접 설계하지 않아도 됩니다.

IP Integration

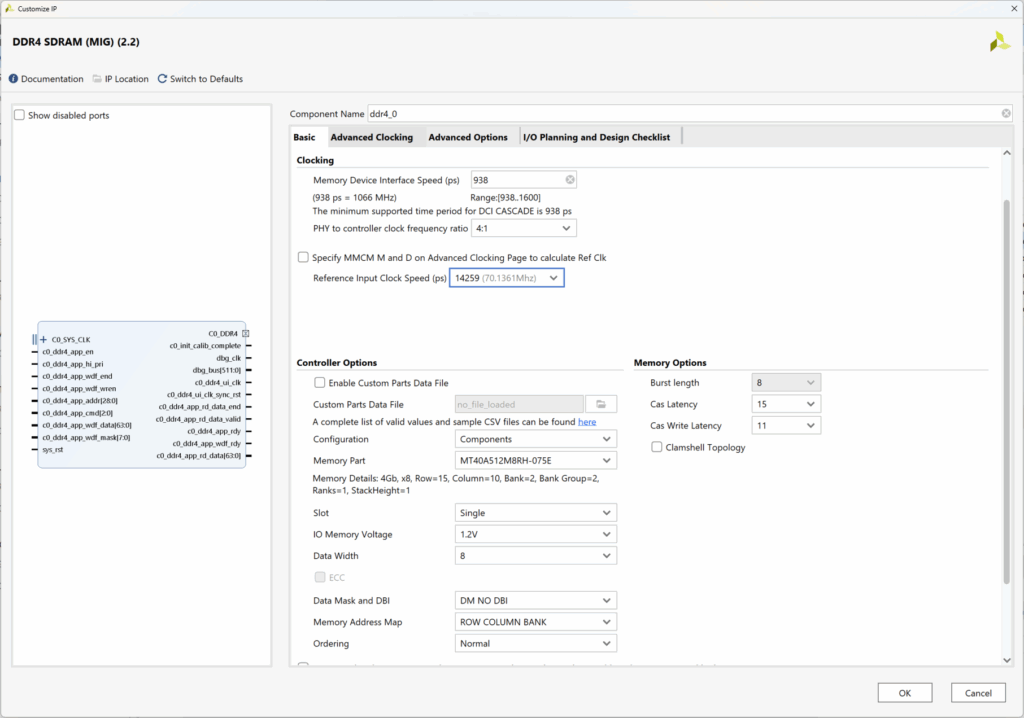

MIG 설정 화면에서는 현재 디바이스에서 구동 가능한 Memory Device Interface Speed를 확인할 수 있습니다. 예를 들어, 1066MHz라면, 1066MHz x 2 = 2132 MT/s가 되며, Data Width가 8비트이므로, 2.132GB/s가 됩니다. 즉, 1개의 DDR 단일 칩을 사용하면, 약 17Gbit/s의 대역폭을 가집니다. 따라서, 대역폭을 늘리기 위해서는 Data Width를 16, 32, 64로 늘려야 합니다.

DDR Efficiency

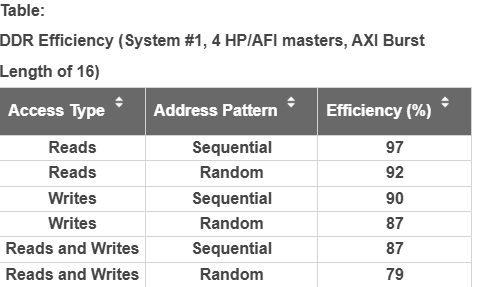

메모리 시스템의 효율성은 여러 요인에 의해 영향을 받습니다. 위에서 계산된 대역폭을 확보했어도, 단일 뱅크 내의 사이클 시간이나, 같은 DDR4 뱅크 그룹에 대해 연속적으로 Activate 명령을 보낼 때 필요한 가격 등이 필요합니다.

가장 좋지 않은 효율을 보이는 경우는 Random 영역에 Read와 Write가 함께 사용되는 경우입니다. 따라서, 애플리케이션에 따른 접근 방식에 따라, 적절한 Bandwidth를 확보해야 합니다.

References

https://www.xilinx.com/support/documents/ip_documentation/mig/v7_1/pg150-ultrascale-mis.pdf

https://docs.amd.com/r/en-US/ug585-zynq-7000-SoC-TRM/Theoretical-Bandwidth