디지털 통신에서 데이터는 ‘0’과 ‘1’의 이진 비트열로 표현됩니다. 하지만 실제 데이터는 무작위적이지 않은 경우가 많으며, 특정 패턴, 특히 긴 연속된 동일 비트(예: ...000000... 또는 ...111111...)를 포함할 수 있습니다. 이러한 패턴은 저속 통신 환경에서는 문제가 되지 않지만, 1Gbps 이상의 고속 통신에서는 치명적인 신호 무결성 문제를 야기합니다. 1Gbps에서 한 비트의 시간은 1나노초(ns)에 불과하므로, 수십 혹은 수백 비트가 연속될 경우 신호의 전압 레벨이 장시간 일정하게 유지됩니다.

비무작위 데이터 패턴의 문제점

이러한 현상은 두 가지 주요한 문제의 원인이 됩니다. 첫째, 신호에 전압 천이(transition)가 사라지게 됩니다. 둘째, 신호의 전력 스펙트럼이 특정 주파수 대역에 집중되어 불필요한 스펙트럼 피크를 생성합니다. 이 두 가지 문제는 연쇄적으로 수신기 성능 저하를 초래합니다. 신호 천이의 부재는 클럭 및 데이터 복구(CDR) 회로를 ‘굶주리게’ 만들어 타이밍 동기화를 상실하게 하고 , 전력 스펙트럼의 집중은 인접 채널과의 혼변조(intermodulation) 및 전자기 간섭(EMI)을 증가시켜 통신 시스템의 규제 준수(예: FCC 기준)를 어렵게 만듭니다. 따라서 비무작위적인 데이터 패턴은 고속 통신 시스템에서 해결해야 할 근본적인 문제입니다.

클럭 및 데이터 복구(CDR)의 성능 저하

고속 통신 시스템에서는 별도의 클럭 라인을 사용하지 않고, 수신기가 들어오는 데이터 스트림 자체의 전압 천이를 감지하여 클럭을 복구합니다. 이 과정은 클럭 및 데이터 복구(CDR) 회로에 의해 수행됩니다. CDR 회로는 데이터의 상승 및 하강 에지에서 타이밍 정보를 추출하여 수신 클럭을 생성하고, 이를 통해 데이터를 정확한 시점에 샘플링합니다.

하지만 데이터에 긴 ‘0’ 또는 ‘1’의 연속 패턴이 포함되어 신호 천이가 부족해지면, CDR 회로는 타이밍 참조를 잃게 됩니다. 이는 클럭 불안정성(timing jitter)을 초래하여 수신 클럭이 데이터 비트와 동기화되지 못하게 만들고, 결국 데이터 샘플링 오류로 이어져 비트 오류율(BER)을 급격히 증가시킵니다. 따라서 고속 통신에서 안정적인 CDR 동작을 보장하기 위해서는 데이터 스트림에 충분한 전이 밀도(transition density)를 확보하는 것이 필수적입니다. 스크램블러는 이러한 문제를 해결하기 위해 데이터 패턴에 관계없이 신호 천이를 증가시켜 CDR 회로가 안정적으로 동기 상태를 유지하도록 돕습니다.

전력 스펙트럼 밀도(PSD)와 전자기 간섭(EMI) 문제

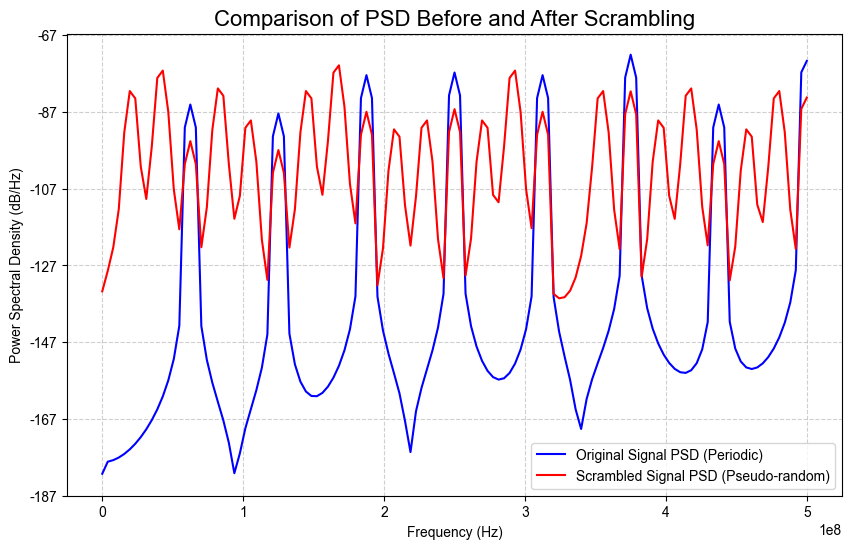

전력 스펙트럼 밀도(PSD)는 신호의 전력이 주파수에 따라 어떻게 분포되어 있는지를 나타내는 척도입니다. 일반적인 디지털 신호는 데이터 패턴에 따라 전력 스펙트럼이 결정됩니다. 특히 비무작위적인 패턴(예: 반복적인 주기 신호)은 신호의 에너지를 특정 주파수 대역에 집중시켜 날카로운 스펙트럼 피크를 형성합니다.

이러한 스펙트럼 피크는 두 가지 심각한 결과를 초래합니다. 첫째, 전력 스펙트럼 밀도에 대한 규제 요건(예: FCC)을 위반할 수 있습니다. 둘째, 이 집중된 에너지는 전자기 방사(electromagnetic radiation)를 유발하여 인접한 통신 채널에 간섭을 일으키는 원인이 됩니다. 이는 고속 직렬 통신에서 심각한 누화(crosstalk) 문제를 야기하여 시스템 신뢰성을 저하시킵니다. 스크램블러는 입력 데이터를 통계적으로 무작위화함으로써 신호의 전력을 넓은 주파수 대역에 고르게 분산시킵니다. 이 과정은 스펙트럼 피크를 제거하고 PSD를 평탄화하여, EMI를 감소시키고 규제 요건을 충족시키는 데 필수적입니다.

스크램블링의 역할: 통계적 화이트닝

스크램블러는 데이터를 암호화하여 메시지를 해독 불가능하게 만드는 보안 장치가 아닙니다. 그 목적은 전송 데이터에 ‘유용한 공학적 특성’을 부여하는 것입니다. 이는 데이터 스트림을 의도적으로 조작하여 통계적으로 무작위적(pseudo-random)인 것처럼 보이게 하는 과정입니다. 이 과정을 흔히 ‘통계적 화이트닝(statistical whitening)’이라고 부릅니다.

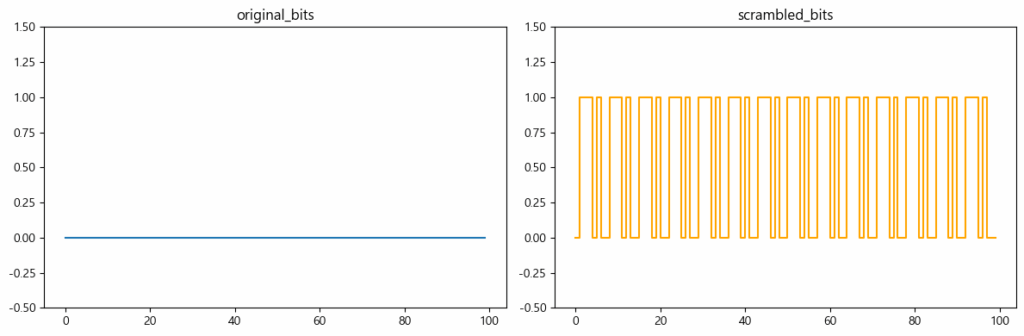

스크램블링은 의사 난수 이진 수열(PRBS, Pseudo-Random Binary Sequence)을 사용하여 원본 데이터 스트림을 수학적으로 변환합니다. 가장 일반적인 구현 방식은 선형 되먹임 시프트 레지스터(LFSR, Linear-Feedback Shift Register)를 사용하여 PRBS를 생성하고, 이를 원본 데이터와 배타적 논리합(XOR) 연산(modulo-2 addition)하는 것입니다. 수신 측의 디스크램블러는 송신기와 동일한 PRBS를 사용하여 XOR 연산을 역으로 적용함으로써 원래의 데이터를 완벽하게 복원합니다.

스크램블링과 라인 코딩의 관계

고속 통신 표준이 발전하면서 스크램블러의 역할은 라인 코딩(line coding)과의 관계 속에서 진화해 왔습니다. 과거의 표준(예: Gen1, Gen2)에서는 8B/10B 인코딩과 같은 라인 코딩 기술이 널리 사용되었습니다. 8B/10B 인코딩은 8비트 데이터를 10비트 심볼로 매핑하여 데이터에 관계없이 충분한 신호 천이를 보장하고, DC 밸런스 및 런 길이(run length) 제한을 통해 신호 무결성을 확보했습니다.

하지만 8B/10B 코딩은 25%라는 상당한 오버헤드(overhead)를 발생시킵니다. 1Gbps 이상의 초고속 환경에서는 이러한 오버헤드가 통신 효율을 크게 떨어뜨리는 단점이 됩니다. 이에 따라 PCI Express Gen3와 같은 최신 표준에서는 8B/10B 코딩을 스크램블링 및 128B/130B 코딩과 같은 훨씬 낮은 오버헤드(약 1.56%)의 조합으로 대체했습니다. 이처럼 1Gbps 이상의 속도에서는 대역폭 효율성이 핵심적인 설계 목표가 되며, 오버헤드가 거의 없는 스크램블러가 신호 무작위성을 확보하는 주요 수단으로 채택되었습니다